# PERFORMANCE AND RELIABILITY OF K<sub>a</sub>-BAND GaAs IMPATT DIODES\*

R. A. Murphy, W. T. Lindley, D. F. Peterson, and P. Staeker

Lincoln Laboratory, Massachusetts Institute of Technology

Lexington, Massachusetts

## Abstract

K<sub>a</sub>-band GaAs p-n junction IMPATT diodes have been fabricated which have delivered 450 mW of added power with 9.6% efficiency at a junction temperature of 275°C. Results of life tests predict operating life in excess of five years at this temperature.

## Introduction

p-n junction GaAs IMPATT diodes have been fabricated for possible use as power amplifiers in the frequency range 36 - 40 GHz in a satellite communications system. Consequently, in addition to satisfactory rf performance, the longevity of these diodes at acceptable operating levels is important. We report here results of thermal, microwave and life testing of these devices.

## Fabrication

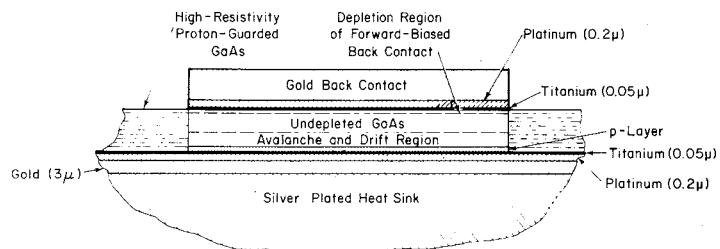

The fabrication procedure of these devices is very similar to that of the Schottky barrier devices, which has previously been described in detail.<sup>1</sup> Although the microwave performance was satisfactory and preliminary life tests encouraging, the Schottky barrier devices demonstrated an instability in the operating voltage when biased to high DC power inputs. Experiments using Auger spectroscopy and x-ray diffraction<sup>2</sup> indicated that this behavior was related to a chemical reaction between Pt and GaAs. Fabrication of p-n junction diodes as shown in Fig. 1 resulted in more stable behavior. The p<sup>+</sup>-layer is approximately 0.3  $\mu$ m thick and is created by the implantation of Cd<sup>+</sup> ions at 400 kV through a 750 Å Si<sub>3</sub>N<sub>4</sub> overcoat and subsequent annealing at 850°C with a SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> overcoat. Two metallizations to the p<sup>+</sup> layer have been examined, and the one shown in Fig. 1, namely Ti-Pt-Au, has proven superior in reliability, as will be discussed later. The other metallization system was Ti-Pt-Ag, which was investigated because of the higher thermal conductivity of silver.

As with the Schottky barrier devices, the heat sinking of the active region is provided by a layer of silver followed by a layer of copper plated over the metallization on the junction (p<sup>+</sup>) side. The GaAs is thinned using reference channels that were etched into the junction side, leaving thin (2.5  $\mu$ m) pockets of GaAs imbedded in the heat sink. The back contact metallization [Ti (900 Å) - Pt (.2  $\mu$ ) - Au (3.5  $\mu$ ) - Ti (1350 Å)] is then sputter deposited, and the back contact pattern is photolithographically defined in the top layer of titanium. The gold and platinum layers are removed by sputter etching in an oxygen atmosphere (20 mTorr Ar, 2 mTorr O<sub>2</sub>) using the titanium as a mask. The titanium mask and the remaining underlying titanium around the contact are removed chemically. The wafer is then proton bombarded, which converts the GaAs to semi-insulating material. The protons do not penetrate the back contact, but convert entirely the surrounding thin layer of GaAs. This both precisely defines the active region of the device and suppresses edge breakdown. The devices are then etched apart and packaged in a conventional pill package.

## Thermal Properties

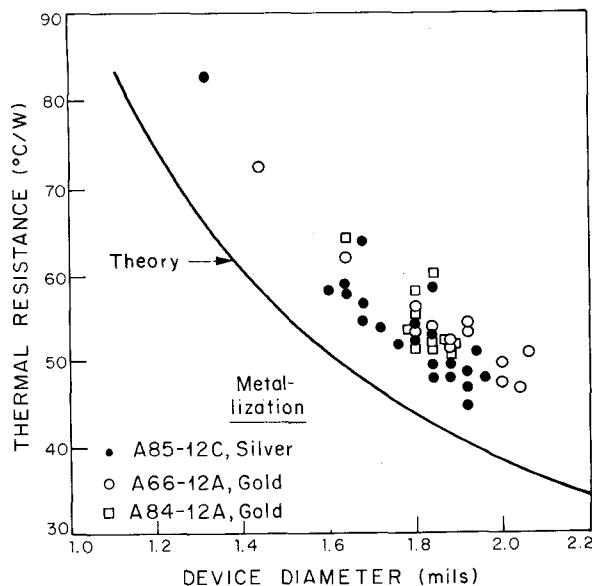

The thermal resistance of a large number of diodes has been measured by standard pulse techniques. Data from

three wafers are shown in Fig. 2 in which the thermal resistance is plotted vs. the device diameter as measured optically during packaging. In spite of the considerable scatter in the data, the thermal resistance of the wafer with the silver metallization appears slightly lower. The solid line is a theoretical estimate of the thermal resistance, which is about 50°C/W less than the measured thermal resistance. The precise reasons for this small discrepancy remain at present unresolved.

## Microwave Performance

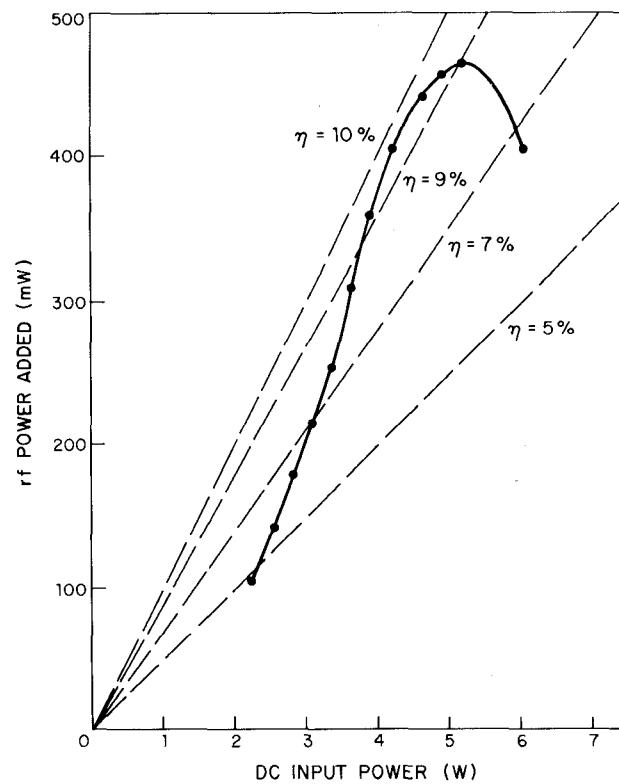

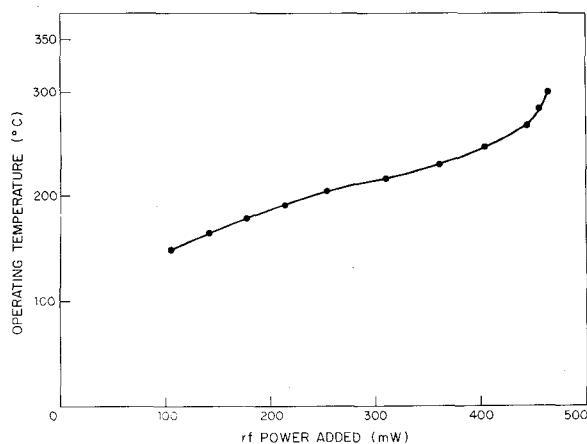

The microwave testing of these diodes is done in a reduced height waveguide circuit in a reflection amplifier configuration. The rf input power is increased until a maximal added power is obtained at a number of DC bias levels, and Fig. 3 shows the resulting data. The peak efficiency is 9.6% and the maximum added power is 470 mW. These numbers are comparable to oscillator results at these frequencies obtained with single-drift IMPATT diodes fabricated from both Si<sup>3</sup> and GaAs.<sup>4</sup> In Fig. 4, the operating temperature, as calculated from the device's thermal resistance, is plotted vs. the rf power added. It can be seen that moderate added powers (e.g. 200 mW) can be achieved at the relatively low junction operating temperatures (e.g. 190°C).

## Life Testing

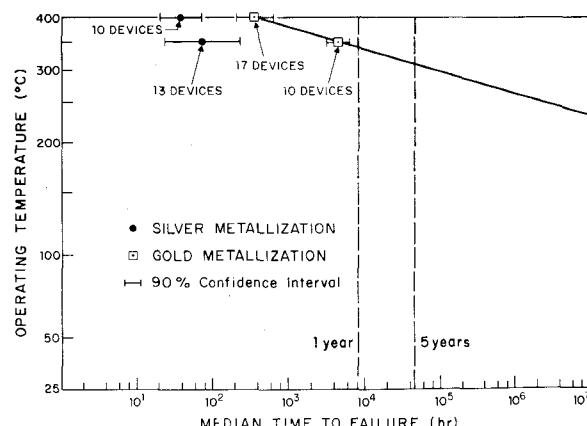

The translation between operating temperature and operational life can be estimated by life tests, which are still continuing. To date, 100 devices from six wafers have accumulated over 150,000 diode test hours. In these tests, devices whose thermal resistance has been measured are raised to the desired junction temperature by adjusting the DC power input. Tests are in progress to ascertain whether the presence of rf oscillations is a factor in device lifetime, but preliminary evidence indicates there is no appreciable effect. All the data presented here were taken in a microwave circuit with rf oscillations suppressed.

An Arrhenius plot of the data obtained thus far is shown in Fig. 5. Here the operating temperature is plotted on a scale proportional to 1/T vs. the median time to failure on a logarithmic scale. The number of diodes in each testing group is shown on the figure. Data from GaAs wafers with the gold metallization and the silver metallization are shown.

The basic assumption involved in extrapolating high temperature results by a straight line on this graph is that the failure-producing phenomena, and hence the times to failure, depend on temperature through the factor  $\exp(E_a/kT)$ . The quantity E<sub>a</sub> is commonly referred to as the activation energy. A large number of physical processes do in fact depend on temperature in this manner, and this relationship has also been verified in a number of semiconductor device lifetime studies. The straight line on Fig. 5 corresponds to an activation energy

\* This work was sponsored by the Department of the Air Force.

of 1.80 eV.

There is, of course, a lack of certainty in an estimate of operating life obtained in this manner. Small statistical errors at high temperatures translate into large errors at lower temperatures. Moreover, the failure mechanism at the lower temperatures of practical interest could be different than that operative at the higher temperatures of the life test, leading to failure times with a different activation energy at the lower temperatures.

From wafers examined to date, it appears that the diodes with the silver metallization are inferior to those with the gold system, having both shorter extrapolated lifetimes and shorter measured lifetimes at higher temperatures. Very long lifetimes are implied by extrapolating the two gold metallization data points, for example, over 200 years at 250°C. Devices are currently under test at lower temperatures which will allow predictions to be made with higher confidence. Although the very long lifetimes predicted at lower temperatures may not be meaningful, much less extrapolation of the data obtained is required in estimating that diode life will exceed moderately long times. For example, the prediction that the diodes will have greater than a five-year lifetime when operated at 275°C or less can be made with greater confidence.

#### Acknowledgements

The authors wish to thank C. M. Wolfe for growing the high mobility epitaxial wafers used to fabricate these devices and J. P. Donnelly for performing the ion implantation and proton bombardment on the many device wafers involved in this study. We are also indebted to G. A. Lincoln for his innovative technical assistance and J. R. Doherty for his efforts in data compilation and reduction.

#### References

1. R. A. Murphy, W. T. Lindley, D. F. Peterson, A. G. Foyt, C. M. Wolfe, C. E. Hurwitz, and J. P. Donnelly, Proc. 1972 Symposium on GaAs (Institute of Physics, London, 1973), p. 224.

2. M. C. Finn, H. Y-P. Hong, W. T. Lindley, R. A. Murphy, E. B. Owens, and A. J. Strauss, Electronic Materials Conf., Las Vegas, Nev., Aug. 27-29, 1973.

3. T. E. Seidel, R. E. Davis, and D. E. Iglesias, Proc. IEEE 59, 1222 (1971).

4. H. P. Weller, IEEE International Electron Devices Meeting, Washington, D.C., Dec. 4-6, 1972 (Paper 12.3).

Fig. 1. Cross-section of a Cd-implanted p-n junction IMPATT diode. The drawing is approximately to scale and shows a device with a Ti-Pt-Au metallization on the p-layer.

Fig. 2. Thermal resistance as a function of device diameter. Data from three wafers with the two different p-layer metallizations are shown, together with a calculated thermal resistance.

Fig. 3. RF performance of a p-n junction device at 37.5 GHz. Lines of constant power added efficiency are shown.

Fig. 4. Necessary operating temperatures for given RF powers added for the diode of Fig. 3.

Fig. 5. Arrhenius curve for p-n junction GaAs IMPATT diodes with the Au and Ag p-layer metallizations.